KiCad ist ein FOSS Softwarepaket, dass zur Entwicklung von elektronischen Schaltungen und das Design der Leiterplatte verwendet werden kann. Es ist seit 2007 in Entwicklung und mittlerweile so weit, dass es zum professionellen Einsatz angewendet werden kann. Das Projekt wird vom CERN unterstützt, die einige neue Funktionen für den Schaltplaneditor, das Backend und den Layouter zur Verfügung gestellt hat.

Für meine kleineren Projekte, habe ich bis jetzt immer nur den Schaltplaneditor verwendet. Bei einem aktuellen Projekt, möchte ich allerdings auch die Leiterplatte herstellen lassen. Dabei soll die Platte im KiCad Layouter entwickelt werden. Diese Artikelserie wird sich mit den Abläufen und Tücken von der Erstellung einer Schaltung, bis hin zur fertigen Leiterplatte befassen. Die Aufteilung der Artikel wird sich an dem Workflow orientieren, den man bei der Erstellung einer Leiterplatte durchläuft. Es wird sich dabei nicht um eine Anleitung zum erstellen von Schaltungen handeln, sondern vielmehr ein Überblick darüber, wie die Arbeit mit KiCad abläuft.

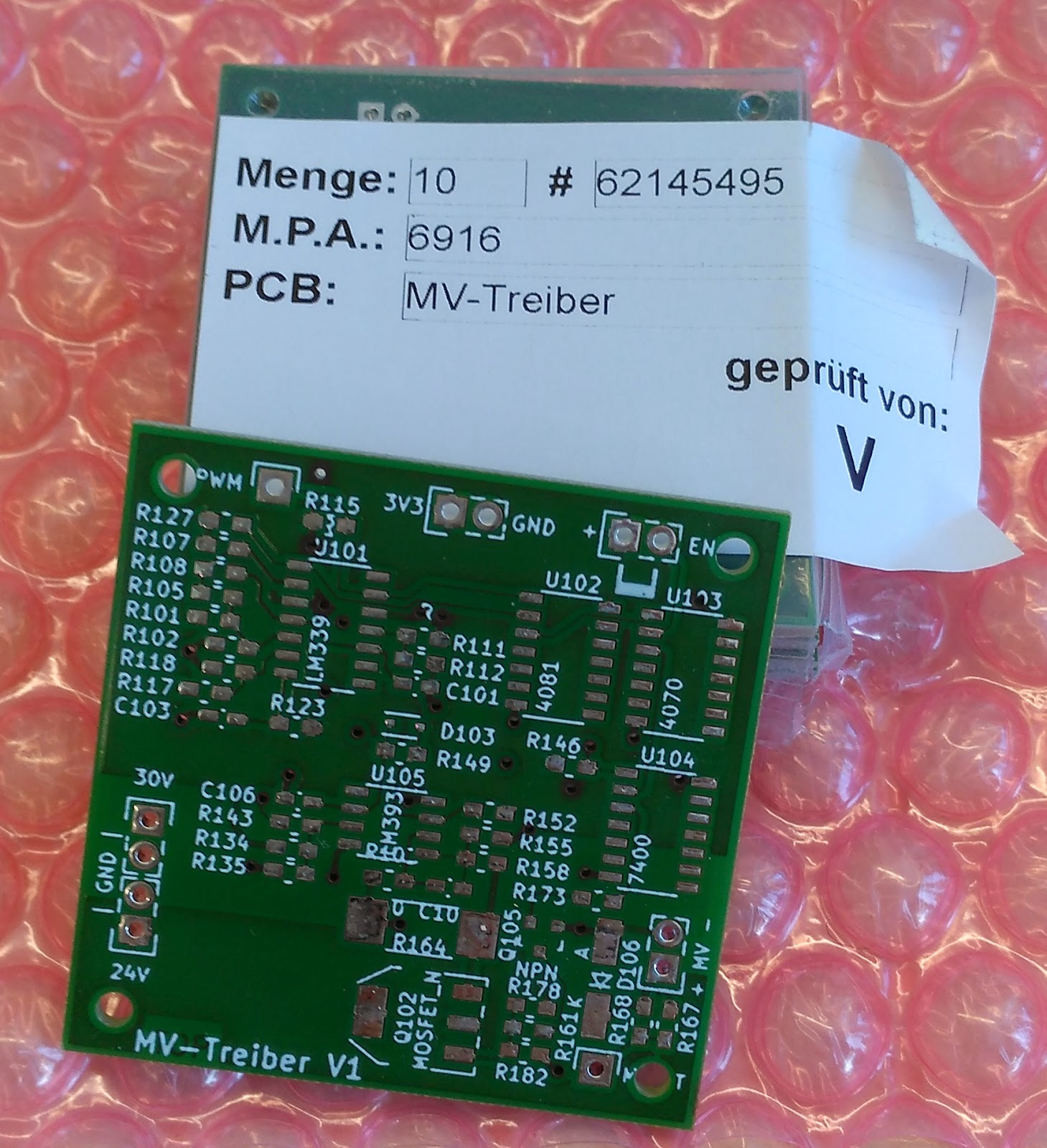

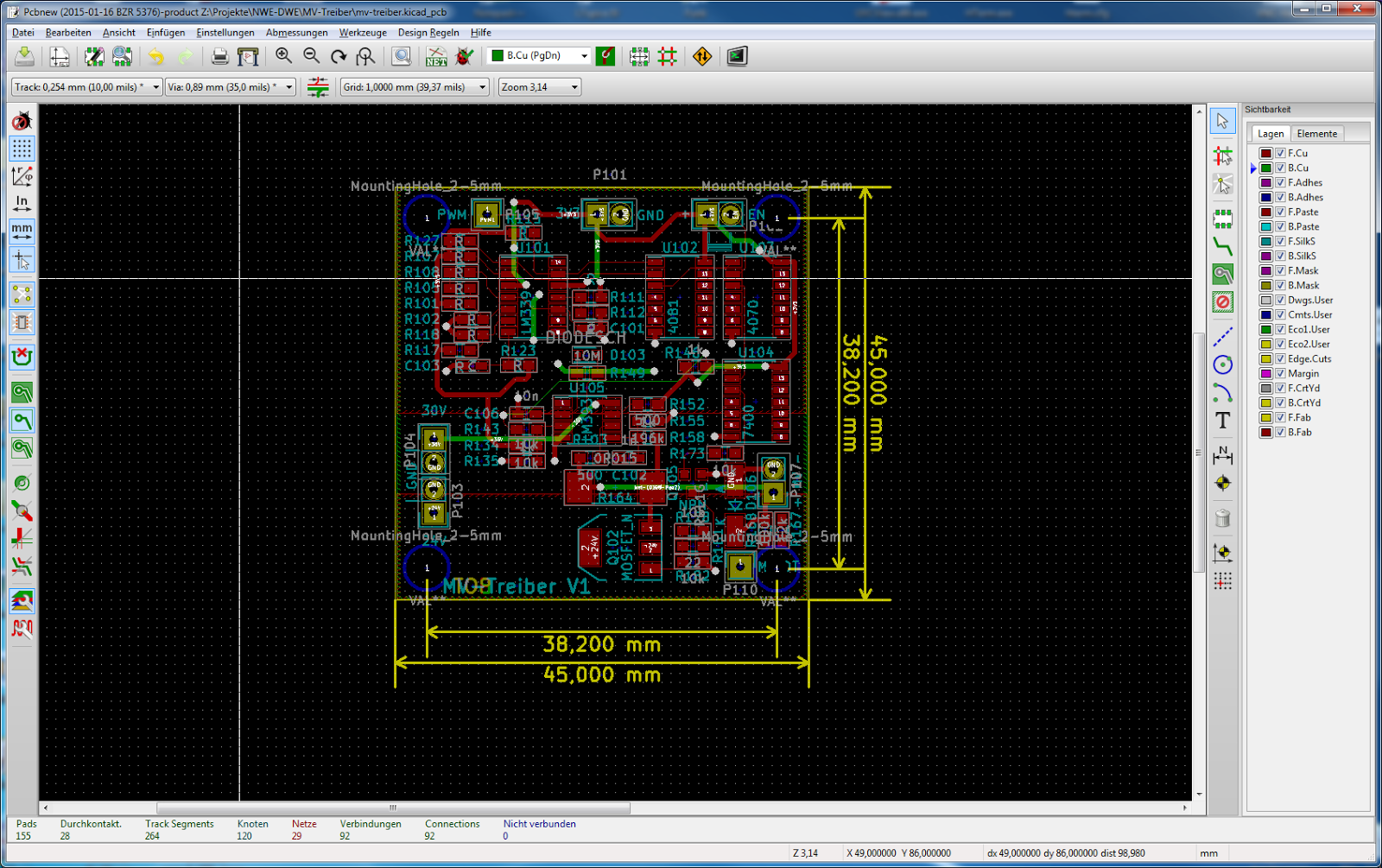

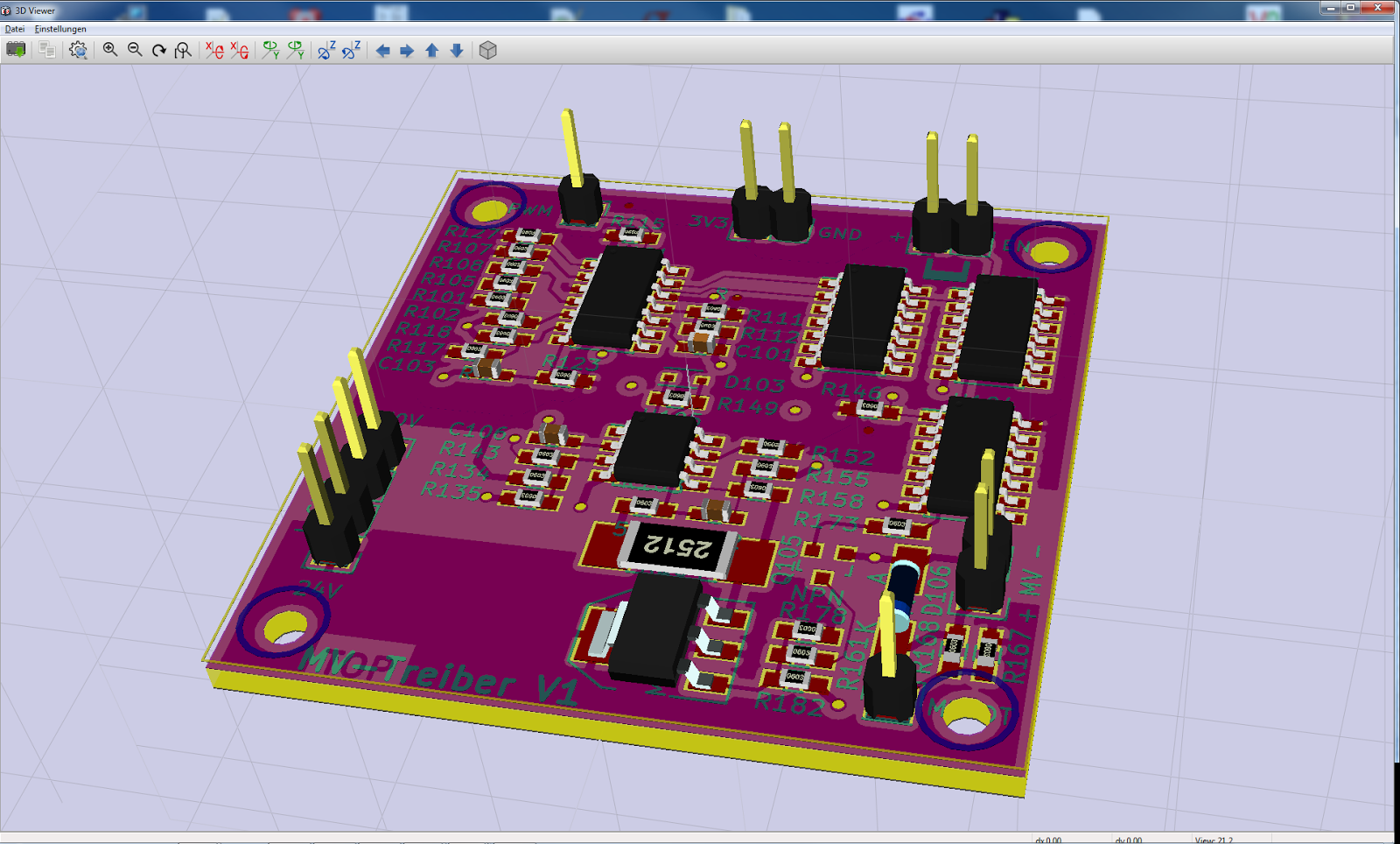

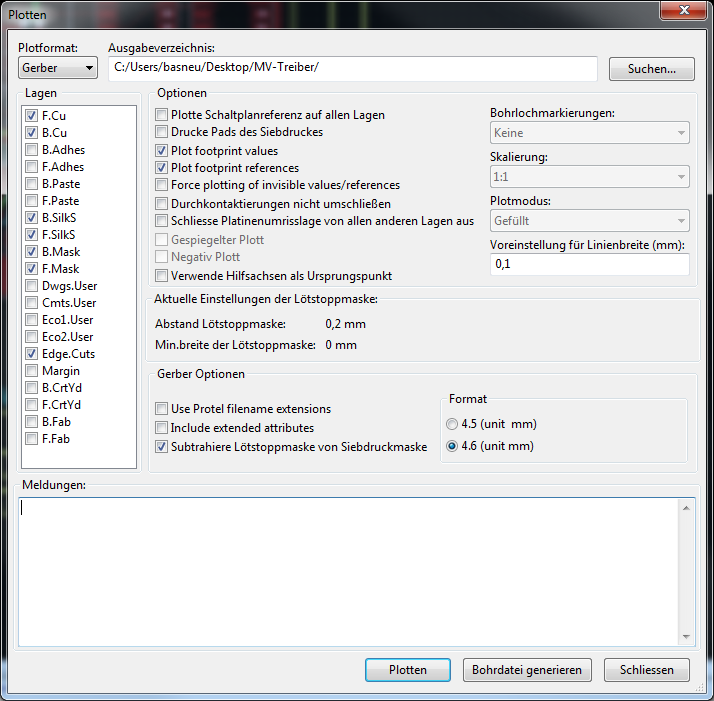

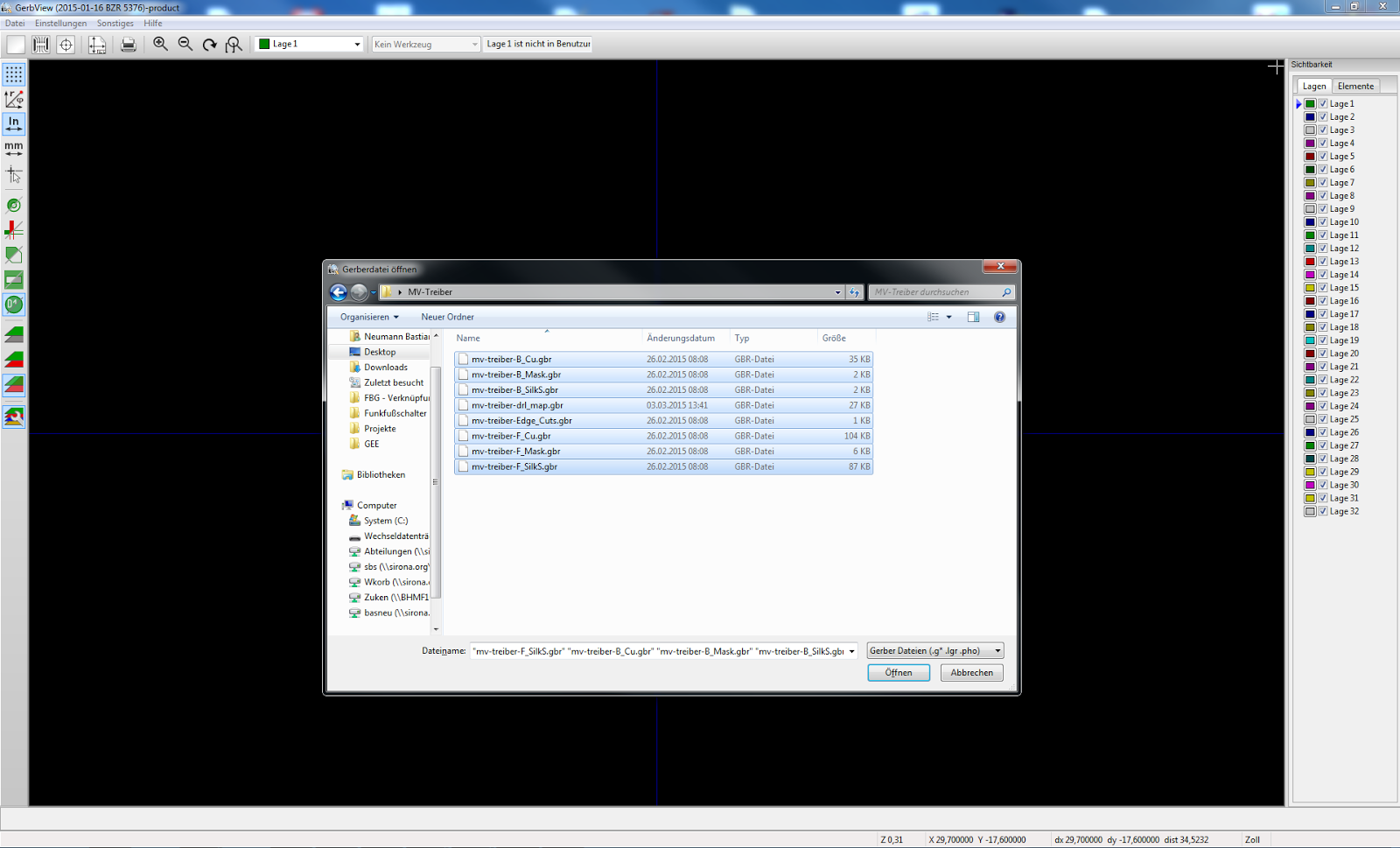

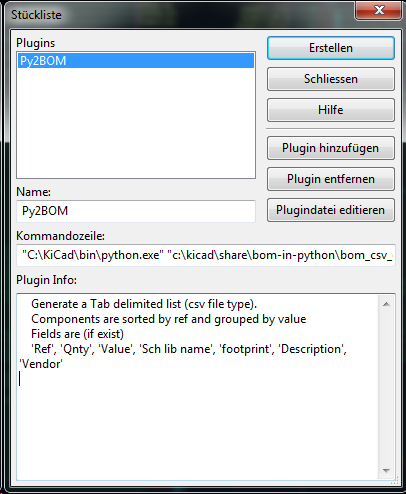

Begonnen wird beim Erstellen des Schaltplans, danach wird die Netzliste erstellt. Diese enthält alle Informationen über die verwendeten Bauteile und deren Eigenschaften (Namen, Pinbelegung und Landepads) sowie Verbindungen. Nebenbei wird die Liste der Bauteile erstellt, die daraufhin zu beschaffen sind. Mit der Netzliste kann dann im dritten Teil die Leiterplatte entworfen werden. Neben der Platzierung der Bauteile werden wir auch die fertigungstechnischen Feinheiten betrachten und den Prozess der Bestellung durchführen. Wenn die Platte dann eingetroffen ist, wird der letzte Artikel, die Bestückung der Platte und das Löten im Reflow-Prozess beschrieben.

KiCad Installieren

Ähnlich wie bei anderen FOSS Projekten, wird KiCad ständig weiterentwickelt und man kann sich die aktuellste Version als Quellcode aus dem Internet herunterladen. Für viele Betriebssysteme gibt es bereits fertige

Binärpakete, die installiert werden können. Zur Zeit sind neue Builds auf

http://kicad.nosoftware.cz/ zu finden. Wer sich die Mühe machen möchte, das Programm selbst zu kompilieren, kann dafür den

Winbuilder verwenden.

Ich beziehe mich in dieser Artikelserie auf die Version 2015-01-17 BZR 5376 aus dem nosoftware.cz Fundus.

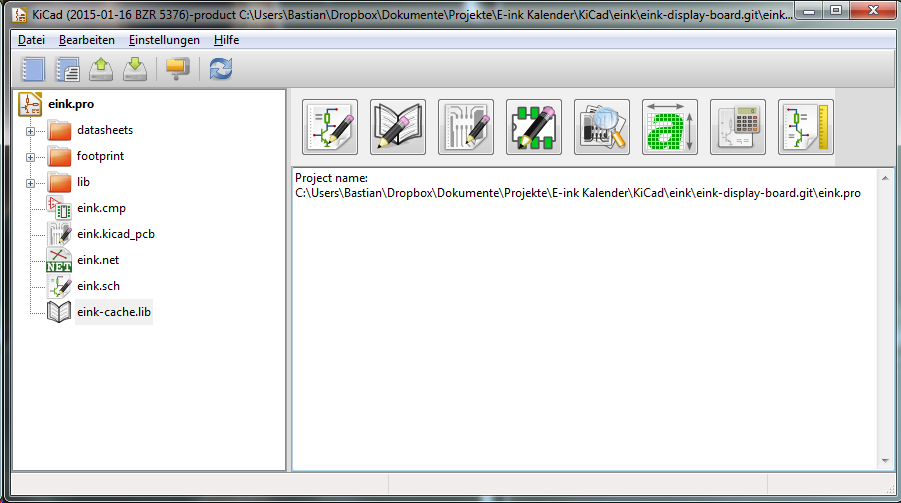

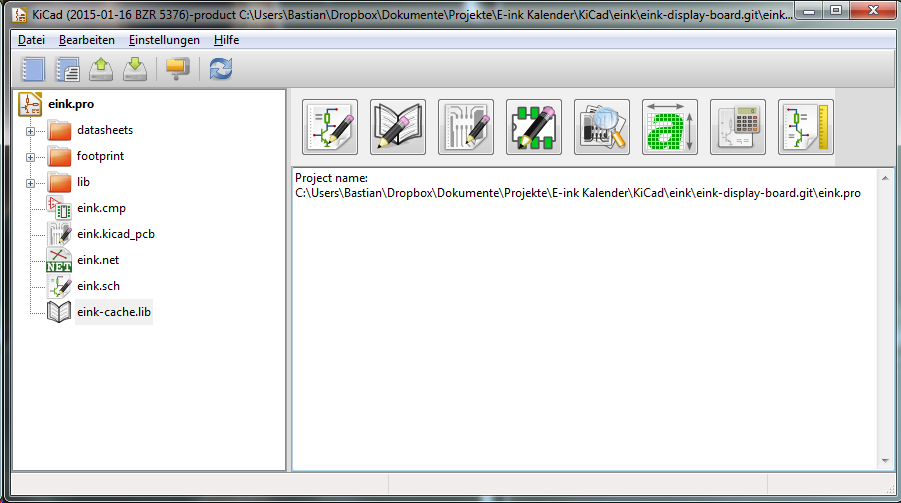

KiCad Manager

Nach dem Start von KiCad wird der Projektmanager gestartet. Dieser zeigt die verwendeten Dateien, des aktuellen Projekts an und bietet eine Schnellstartleiste für die benötigten Programme, wie Schaltplan- und Symboleditor, oder Layouter. Weiterhin sind noch einige kleine Tools, wie Bitmap zu Komponenten-Konvertierung, Berechnungs-Tools und Schaltplan-Layouteditor.

Von diesem Fenster aus wird ein Projekt verwaltet.

Der Schaltplaneditor

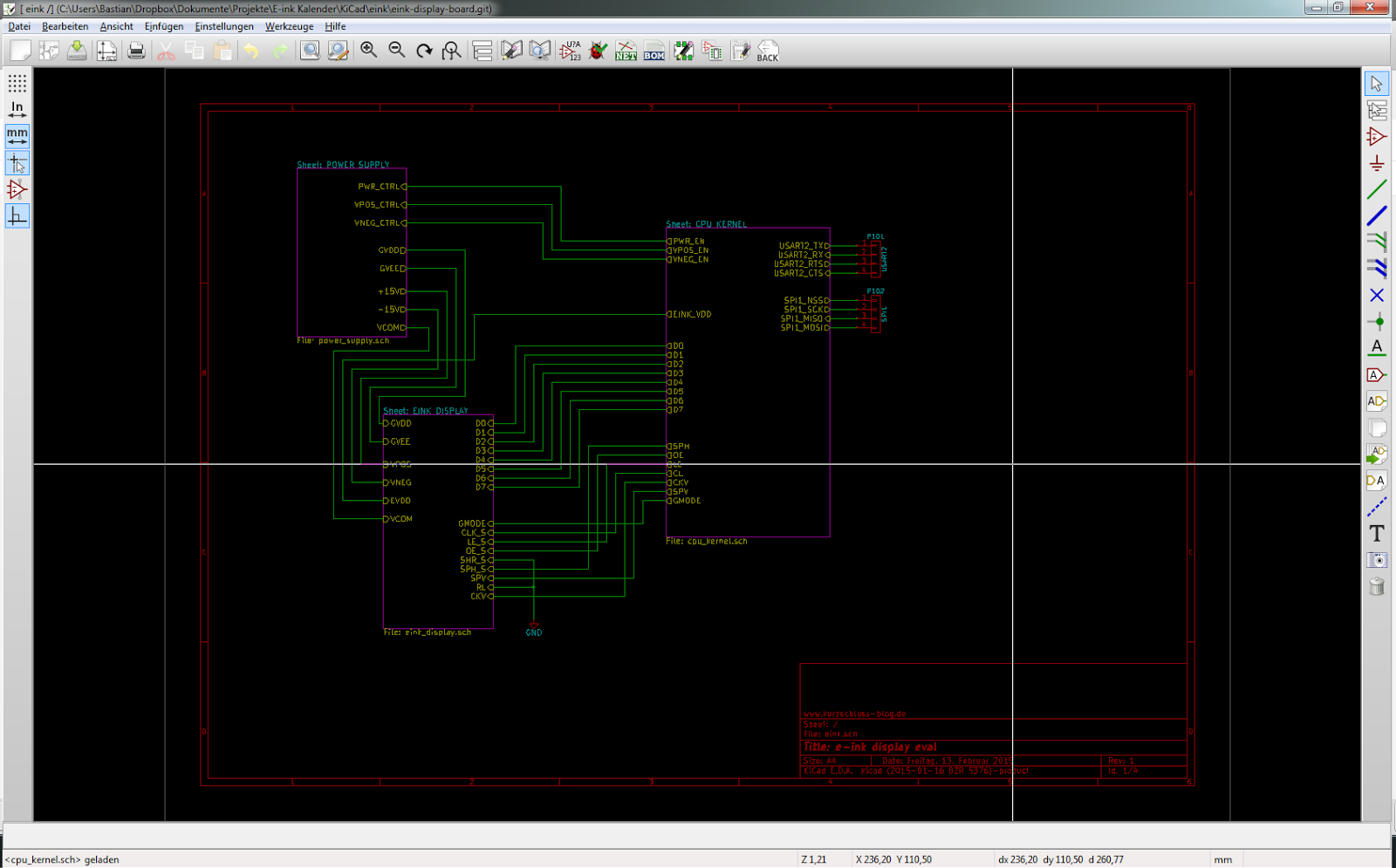

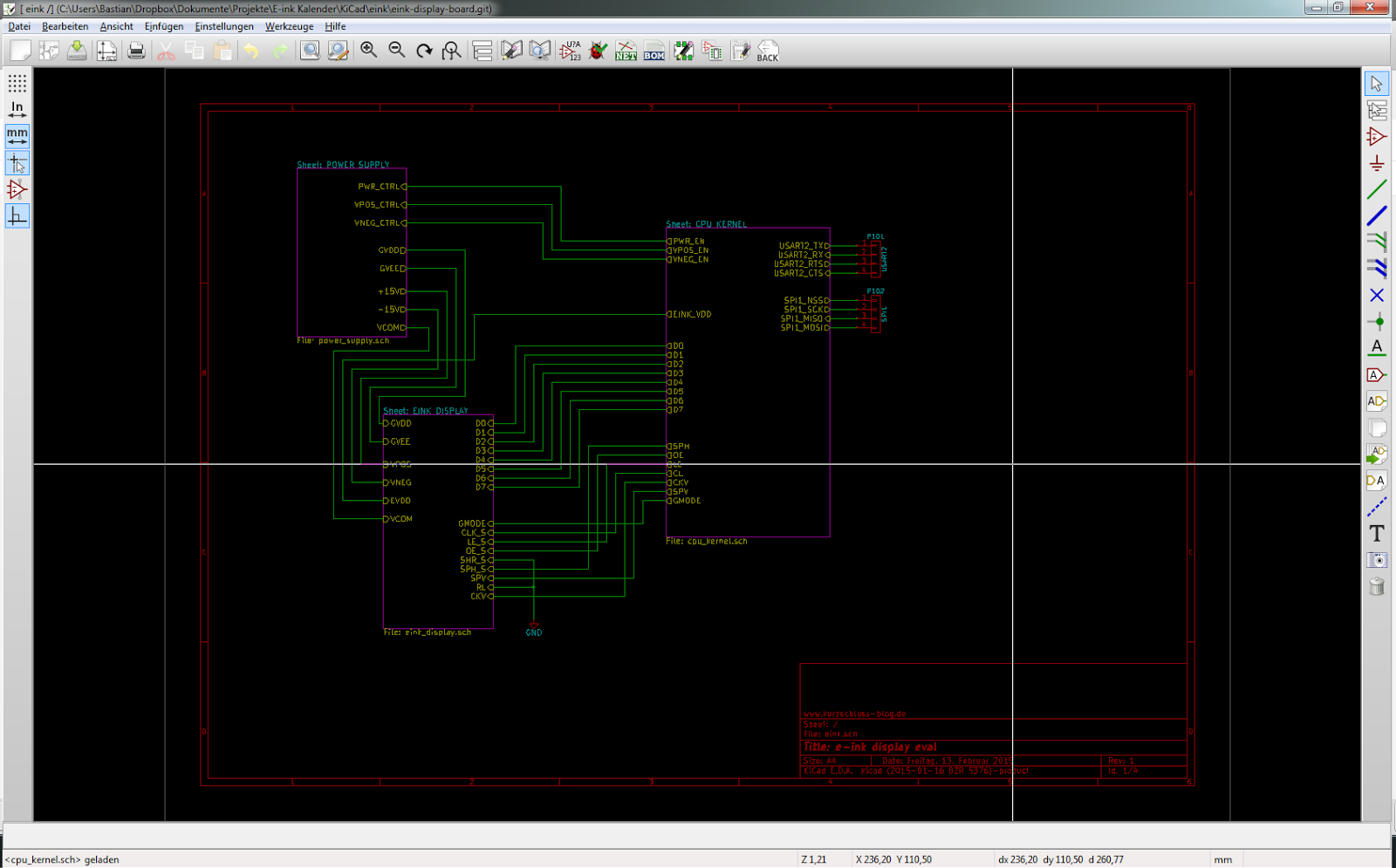

Der Schaltplan wird über den Editor Eeschema erstellt. Die Abbildung zeigt den fertigen Schaltplan eines Projekts. Die Übersichtsseite des Schaltplans, also die erste Seite ist hier wie ein Blockschaltbild zu betrachten. Verschiedene Funktionen sind in einzelne Blätter (Subsheets) aufgeteilt. Das muss man nicht unbedingt machen, es macht die Schaltung ab einer gewissen Größe allerdings übersichtlicher. Ich habe meine Schaltungen eigentlich immer auf A3-Größe festgelegt und gehe von dort aus in Subsheets um die Komplexität der einzelnen Komponenten geringer zu halten. Um Signale zwischen den einzelnen Blättern austauschen zu können, werden hierarchische Labels verwendet. Zwei unterschiedliche Netze, die mit einem gleichnamigen Label verbunden werden, sind danach das gleiche Netz. Auf dem Hauptblatt sieht man dann die Verbindungen der einzelnen Untergruppen. Somit wird die Logik abstrahiert und einfacher auf den ersten Blick zu verstehen.

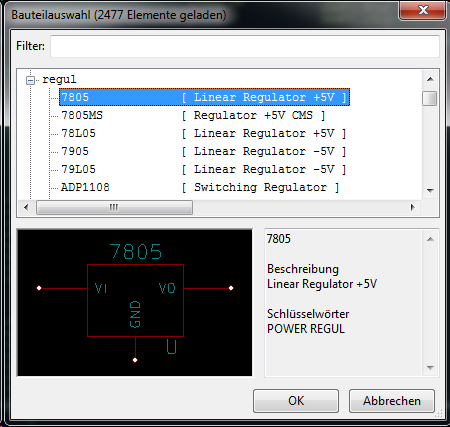

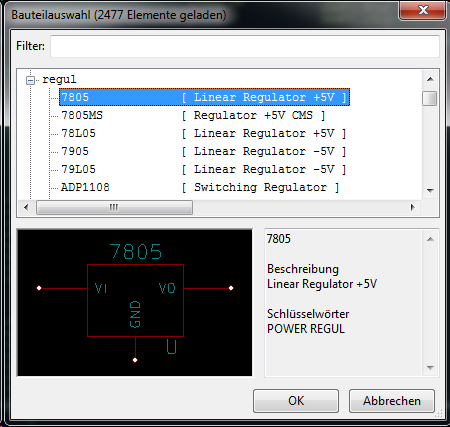

Ein Schaltplan besteht aber nicht nur aus Subsheets, sondern auch aus Komponenten, die die eigentliche Schaltung darstellen. Diese werden über das ‚Bauteil hinzufügen‘ Menü ausgewählt und in den Schaltplan eingefügt. Das Menü erscheint, wenn man das Bauteil-Werkzeug ausgewählt hat und in den Schaltplan klickt. Hier sind alle Bauteile, die in der Bibliothek abgelegt sind zu finden. Über die Filter Eingabe kann nach eine bestimmten Teil gesucht werden, über das Auswahlmenü können die einzelnen Bibliotheken durchsucht werden. Der untere Bereich dient als Vorschau für die Komponente und gibt zusätzliche Informationen zu dem Bauteil, sofern diese bei der Erstellung hinterlegt wurden. Das gewählte Bauteil kann nach dem Drücken des OK-Buttons in den Schaltplan eingefügt werden.

Sollte ein Bauteil nicht in der Bibliothek zu finden sein, muss es neu angelegt werden. Es sind zwar mittlerweile eine

Vielzahl von

Bauteilbibliotheken im Internet zu finden, doch es kann vorkommen, dass es dieses eine Bauteil mit diesem Gehäuse und diesem Pinout eben noch nicht gibt. Der Bauteil-Editor von KiCad ist allerdings einfach zu benutzen, wenn man das System hinter den Bibliotheken einmal verstanden hat. Eine Bibliothek ist eine Datei. In dieser Datei befinden sich Beschreibungen für eine oder mehrere Bauteile. Die Bibliotheksdatei muss in einem KiCad bekannten Verzeichnis liegen und zusätzlich noch als aktive Bibliothek ausgewählt werden. Erst dann ist sie in der Bauteil-Auswahl verfügbar. Die erzeugten Biblioteks-Dateien sind im Textformat gespeichert. Diese Eigenschaft machen wir uns später zu Nutze, wenn es darum geht verschiedene Versionen zu verwalten.

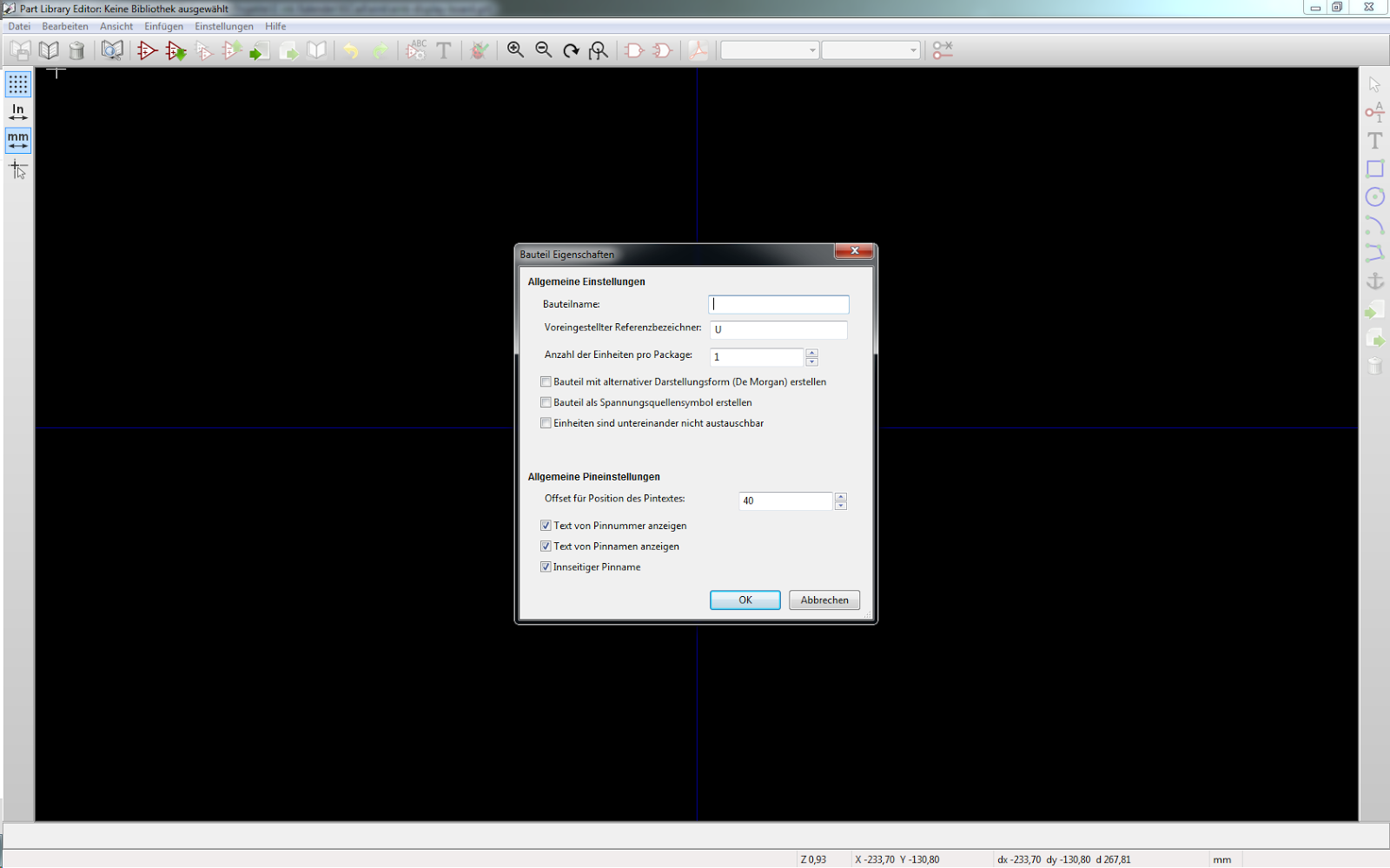

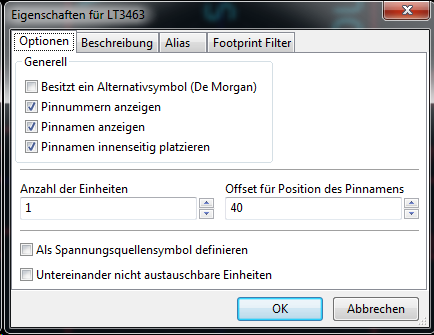

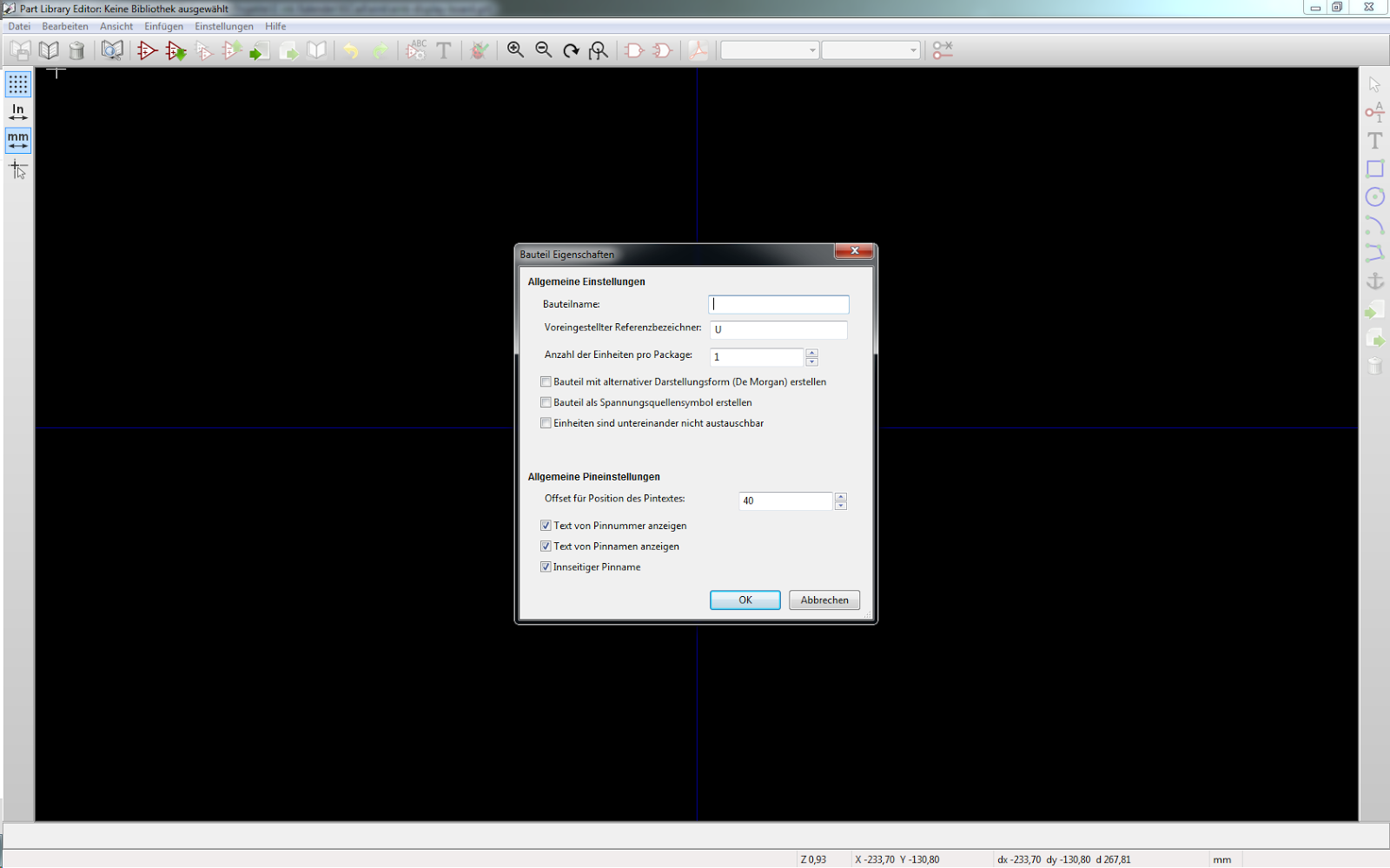

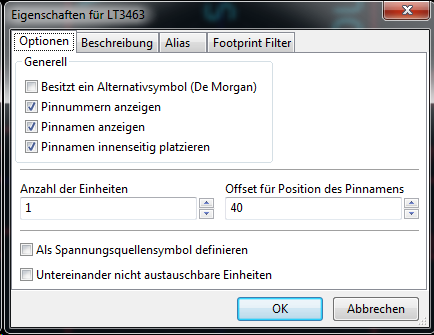

Das neue Bauteil bekommt einen Namen. Es wird festgelegt, welche Bezeichner für das Bauteil verwendet werden soll (R für Widerstände, L für Induktivitäten, C für Kondensatoren, V für Dioden, usw.) und die Anzahl der Komponenten pro Bauteil (bspw. für Dual-FETs oder Widerstandsarrays).

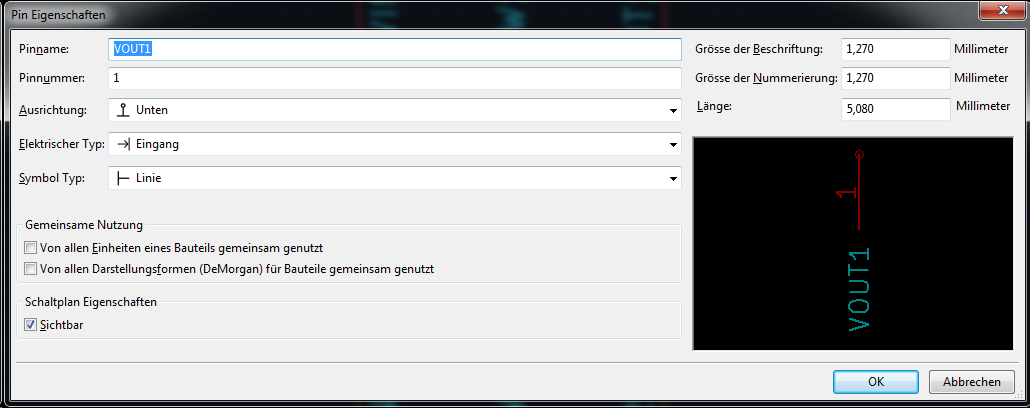

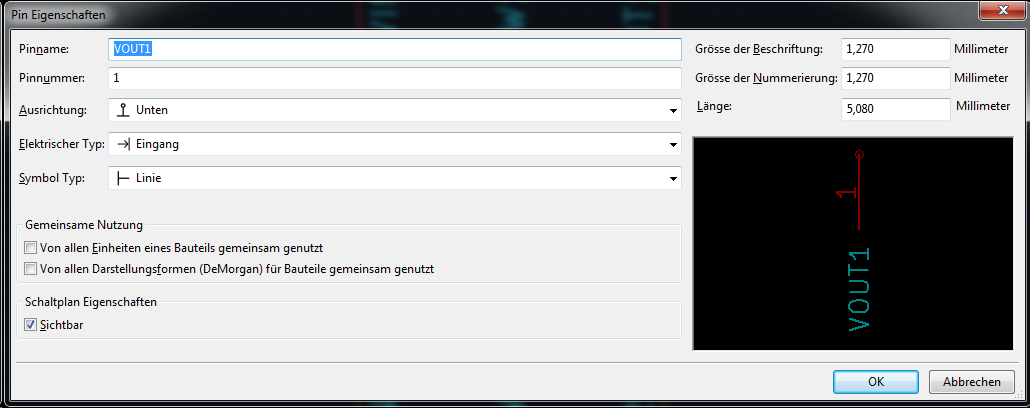

Daraufhin kann das Bauteil gezeichnet werden und die Pins eingefügt, benamt und benummert werden. Wichtig ist festzulegen, wie der Energiefluss der Pins ist. Hier sollte Jeder Versorgungspin (VCC, GND, …) als Eingang, jeder Ausgangspin als Ausgang (Vout, …) und jeder Controller-Pin als Bidirektional festgelegt werden. Man kann hier noch weiter ins Detail gehen, wenn man das möchte. Die grobe Festlegung des Energieflusses ist aber wichtig um spätere Fehler im Design Rule Check (DRC) zu vermeiden.

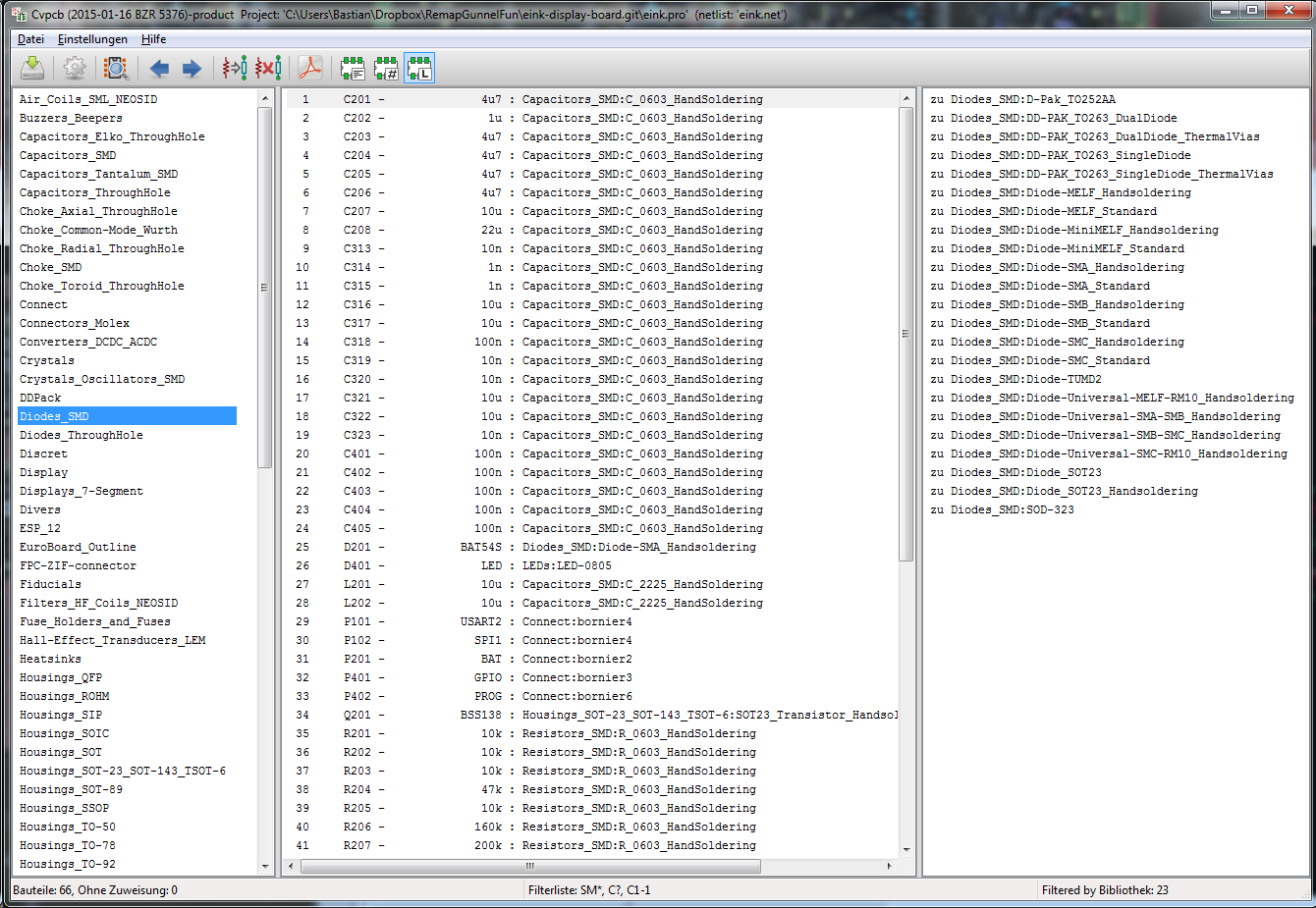

In den Eigenschaften des Bauteils, können für später wichtige Informationen hinterlegt werden. Einmal grundsätzliche Eigenschaften zur Darstellung des Symbols, ähnlich der Einstellungen beim Erstellen des neuen Symbols. Eine Beschreibung das Bauteils und das Datenblatt sollten nicht fehlen, so kann während der Schaltplaneingabe schnell auf das Datenblatt zugegriffen werden. Für viele Bauteile gibt es unterschiedliche Beschreibungen, die mit der eigentlichen Funktion des Bauteils nicht viel zu tun haben (Gehäuseform, Verpackungseinheiten, …). Außerdem gibt es Bauteile, die von verschiedenen Herstellern geliefert werden, aber die gleiche Beschaltung und Funktion aufweisen. So können dem Bauteil Aliase vergeben werden, um es unter diesen Namen in der Liste der Komponenten zu finden. Obwohl im Schaltplaneditor keine fixe Verbindung von Schaltplakomponente und physikalischem Bauteil besteht, kann dem Bauteil eine Reihe von Landungspads (Footprints) für die Leiterplatte mitgegeben werden. Das erleichtert später die Zuweisung von Bauteilform zu Bauteil.

Bauteile-Bezeichner

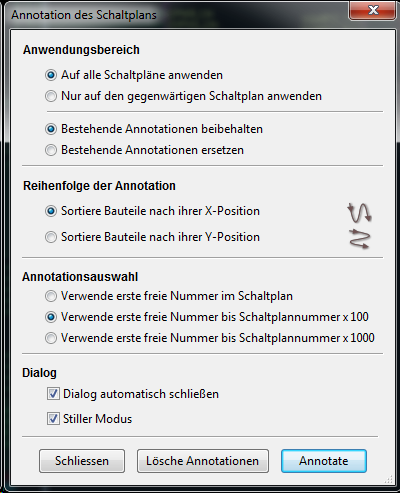

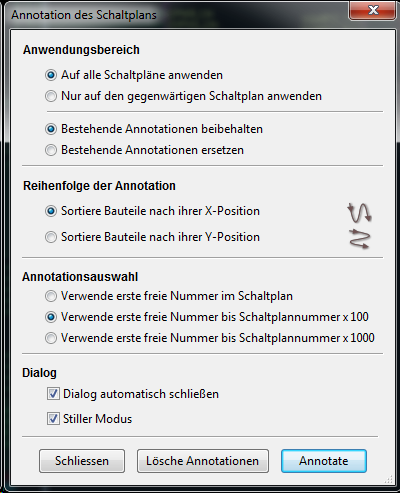

Nachdem der Schaltplan in den Editor eingegeben wurde, oder schon währenddessen kann der Komponente ein Bezeichner zugewiesen werden. Beim Erstellen des Symbols haben wir gesehen, dass jedes Symbol einen Prefix besitzt, der die Art des Bausteins beschreibt (R, L, C, V, …). Dazu kommt dann meistens noch eine Nummer, die das Bauteil eindeutig kennzeichnet. So entsteht dann der Widerstand R100 oder der Kondensator C371. Die Bezeichnung kann manuell beim Hinzufügen des Symbols erfolgen, oder automatisch mit dem Annotation-Tool. Dieses Tool erlaubt es uns entweder alle, oder alle noch nicht benannten Bauteile mit den nächsten freien Nummern zu benennen. Dabei kann der aktuelle Schaltplan, oder alle Schaltpläne des Projekts beachtet werden. Die nächstmögliche freie Zahl ist aber auf das ganze Projekt bezogen, denn jeder Bezeichner darf nur einmal vorkommen.

Das Annotationstool besitzt die Möglichkeit, die zu benennenden Bauteile entweder waagerecht, oder senkrecht zu ermitteln und zu bezeichnen. Ich habe eigentlich immer die senkrechte Reihenfolge gewählt. Der nächste Punkt, die Annotationsauswahl, lässt es zu, dass wir Blatt abhängig die Bezeichnung der Bauteile erhöhen. So wird der erste Widerstand auf Blatt 3 mit 300 bezeichnet, der zweite mir R301 usw. Später hilft das den Widerstand von der Leiterplatte wieder in den Subsheets zu finden. Das ist vor allem im Fehlerfall praktisch.

DRC

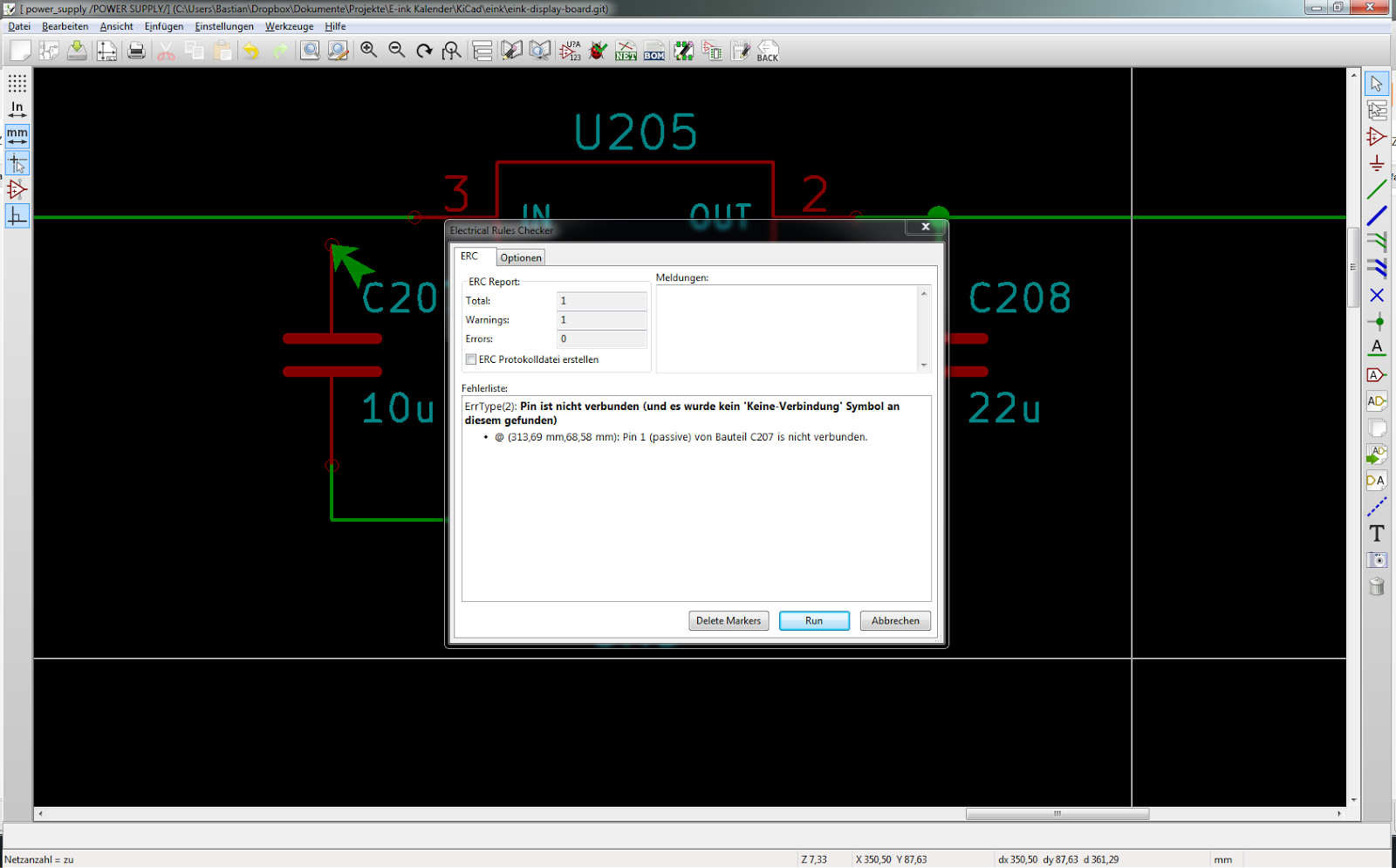

Der Design Rules Check ist ein sehr hilfreiches Tool beim verifizieren der Schaltung. Er schaut sich den kompletten Schaltplan an und bestimmt anhand von gegebenen Bedingungen, ob der Schaltplan so regelkonform ist. Diese Regeln werden in den Optionen festgelegt. Das Bild zeigt einen typischen Fehler; Ein Pin eines Bauteils ist nicht angeschlossen und der Pin wurde nicht explizit, als nicht verbunden gekennzeichnet. Im Schaltplan wurde die Stelle markiert und wird beim Klick auf den Fehler in der Fehlerliste hervorgehoben. Allerdings ist das nur ein Warnhinweis und kann ignoriert werden. In den Optionen des DRC kann festgelegt werden, wie mit verschiedenen Bedingungen umgegangen werden soll. Beispielsweise ist es OK zwei Eingangspins oder Tri-State-Pins miteinander zu verbinden, aber wenn zwei Ausgangspins verbunden werden, wird ein Fehler erzeugt. Diese Regeln sind nicht verpflichtend, können aber helfen, dass beim eingeben des Schaltplans keine Fehler gemacht wurden.

Zusammenfassung

Der Schaltplan wird in EEschema eingegeben. Dabei werden Symbole aus einer Bibliothek verwendet. Diese Symbole sind nicht zwangsweise an ein Physikalisches Bauteil gebunden. Die Bibliothek ist eine Textdatei in der alle zu dieser Bibliothek gehörenden Symbole hinterlegt sind.

Komplexe Schaltungen können auf Subsheets ausgelagert werden. Diese können Signale mit hierarchischen Labels austauschen. Das Bezeichnen von Komponenten kann manuell oder mit dem Annotationstool gemacht werden. Am Ende kann mit dem DRC ermittelt werden, ob noch grobe Fehler im Schaltplan zu finden sind.

Wie die virtuellen Komponenten im Schaltplan zu ihren physikalischen Gegenstücken umgewandelt werden, warum ein Widerstand auch ein wichtiges Bauteil ist, warum es sinnvoll ist Schaltplansymbol und physikalisches Bauteil zu trennen und was die Netzliste macht, betrachten wir dann im

nächsten Beitrag.